# EVB-LAN9668 Evaluation Board User's Guide

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">https://www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMA-TION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON- INFRINGEMENT, MERCHANTABILITY, AND FIT-NESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI- RECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM, net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, KoD, maxCrypto, maxView, memBrain, Mindi, MiVi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2022, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-6683-0690-1

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# EVB-LAN9668 EVALUATION BOARD USER'S GUIDE

# **Table of Contents**

| Preface                                                                                               | 7  |

|-------------------------------------------------------------------------------------------------------|----|

| Introduction                                                                                          | 7  |

| Document Layout                                                                                       | 7  |

| Conventions Used in this Guide                                                                        | 8  |

| Warranty Registration                                                                                 | 9  |

| The Microchip Website                                                                                 | 9  |

| Development Systems Customer Change Notification Service                                              |    |

| Customer Support                                                                                      |    |

| Document Revision History                                                                             |    |

| Chapter 1. Overview                                                                                   |    |

| • 1.1 Introduction                                                                                    | 11 |

| 1.1.1 Audience                                                                                        |    |

| 1.1.2 References                                                                                      |    |

| 1.1.2.1 Microchip Documents                                                                           |    |

| 1.1.2.2 IEEE Standards                                                                                |    |

| 1.1.3 Terms and Abbreviations                                                                         |    |

| 1.2 Features                                                                                          |    |

| 1.2.1 Feature List                                                                                    |    |

| 1.2.2 CPU System                                                                                      |    |

| 1.2.2.1 Embedded ARM <sup>®</sup> Cortex <sup>®</sup> A7 CPU System<br>1.2.2.2 External CPU Connector |    |

| 1.2.3 Management and User I/O                                                                         |    |

| 1.2.4 CuPHYs                                                                                          |    |

| 1.2.5 Timing and Synchronization                                                                      |    |

| 1.2.5.1 SyncE                                                                                         |    |

| 1.2.5.2 PTP/IEEE1588v2                                                                                |    |

| Chapter 2. Management Software                                                                        |    |

|                                                                                                       | 15 |

| 2.1 Introduction                                                                                      |    |

| 2.2 CLI for Management and Debugging                                                                  |    |

| 2.3 WebGUI for Management                                                                             |    |

| Chapter 3. Board Details                                                                              |    |

| 3.1 EVB-LAN9668 Reference Board                                                                       |    |

| 3.1.1 Board Overview                                                                                  |    |

| 3.1.2 Power DC Input and LED                                                                          |    |

| 3.1.3 Reset Button and LED                                                                            |    |

| 3.1.4 System Status LED                                                                               |    |

| 3.1.5 Front Port Layout and LEDs<br>3.1.6 Rear SMA Connectors                                         |    |

| 3.1.7 USB 2.0 Serial Port                                                                             |    |

|                                                                                                       |    |

| 3.1.8 PCIe <sup>®</sup> 2.0 End Point      | 21 |

|--------------------------------------------|----|

| 3.1.9 ARM <sup>®</sup> CPU JTAG Connector  |    |

| 3.1.10 Expansion Header                    |    |

| 3.1.11 Boot Modes and Reference Clock      |    |

| Chapter 4. Hardware Details                |    |

| 4.1 Block Diagrams                         |    |

| 4.2 LAN9668 VCORE CPU System               |    |

| 4.2.1 Boot Mode Strapping                  |    |

| 4.2.2 PLL Strapping                        | 25 |

| 4.2.3 DDR3L SDRAM                          |    |

| 4.2.4 SPI NOR Flash Device                 |    |

| 4.2.5 SPI NOR Flash Programming            |    |

| 4.2.6 e-MMC™ Flash Device, Bulk Storage    | 26 |

| 4.2.7 PHY Interrupts                       |    |

| 4.2.8 Micro USB Serial Port                |    |

| 4.2.9 PCIe <sup>®</sup> 2.0 End Point      |    |

| 4.2.10 ARM <sup>®</sup> CPU JTAG Connector |    |

| 4.2.11 Expansion Header                    |    |

| 4.2.12 GPIO Overview Usage                 | 30 |

| 4.3 Ethernet Ports                         |    |

| 4.3.1 Port Mapping                         |    |

| 4.3.2 PHY Copper Interface                 | 32 |

| 4.3.3 ICM - Integrated Magnetics           | 32 |

| 4.3.4 MII-Management                       | 32 |

| 4.3.5 Thermal Diode (Optional)             | 33 |

| 4.3.6 Port LEDs and COMA Signal            |    |

| 4.3.7 Optional Clock Scheme                | 33 |

| 4.4 Timing and Synchronization             | 33 |

| 4.4.1 SyncE                                | 33 |

| 4.4.2 Recovered Clock Multiplexing         |    |

| 4.4.3 PTP/IEEE1588v2                       | 34 |

| 4.4.4 ZL30772 Frequency Plan               | 34 |

| 4.4.5 SMA Connectors                       | 35 |

| 4.5 Reset and Reset Button                 |    |

| 4.6 Power Supply                           |    |

| 4.6.1 DC/DC Converters                     |    |

| 4.6.2 Power Supply Sequencing              |    |

| Chapter 5. PCB Layout                      |    |

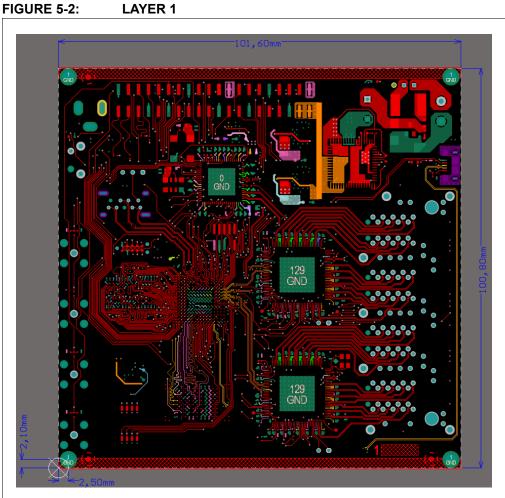

| 5.1 Introduction                           | 39 |

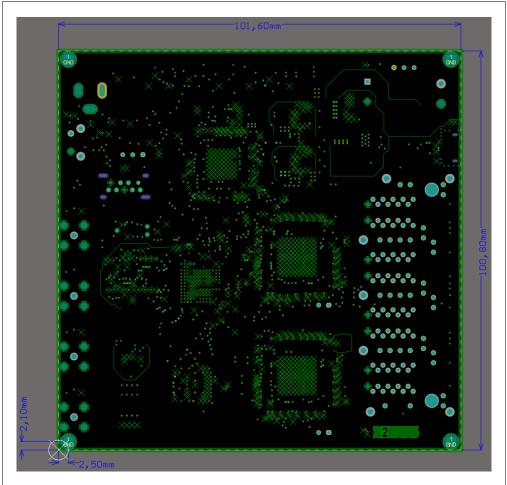

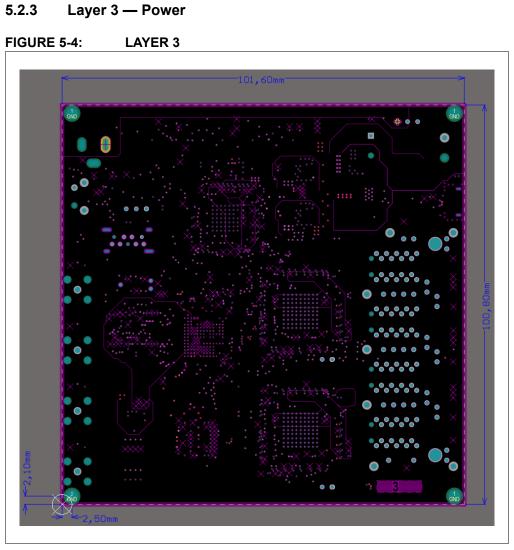

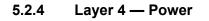

| 5.2 PCB Layers                             | 40 |

| 5.2.1 Layer 1 — Top                        |    |

| 5.2.2 Layer 2 — Ground Plane               | 41 |

| 5.2.3 Layer 3 — Power                      |    |

| 5.2.4 Layer 4 — Power                      | 43 |

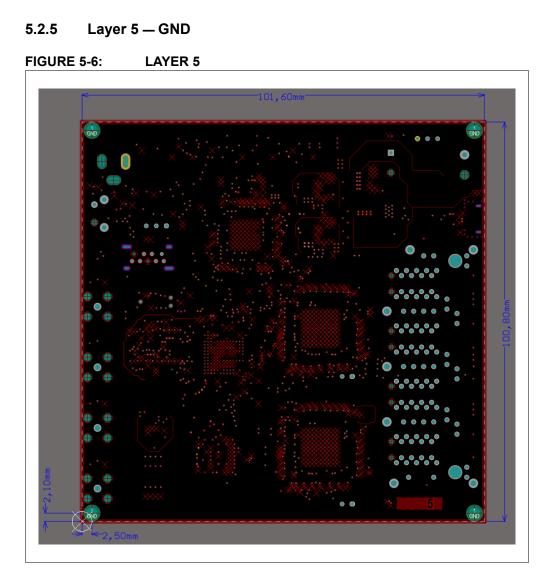

| 5.2.5 Layer 5 — GND                        | 44 |

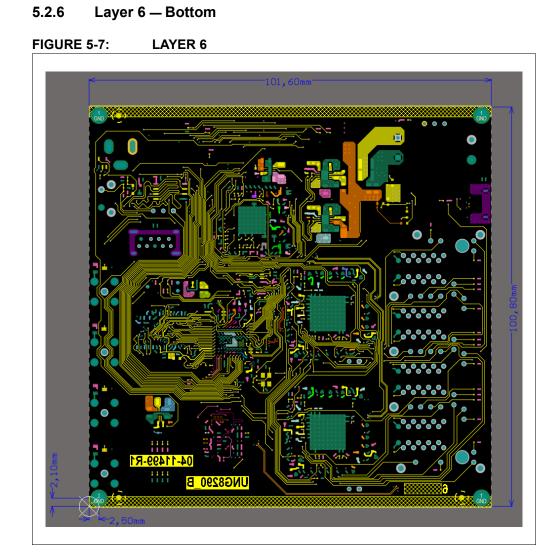

| 5.2.6 Layer 6 — Bottom                     | 45 |

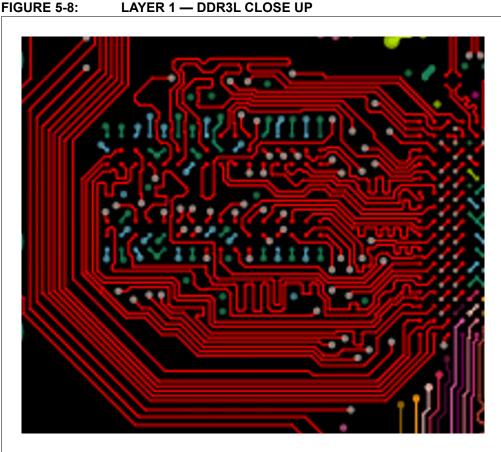

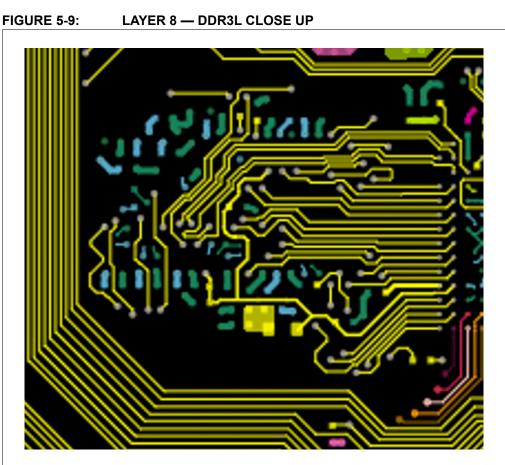

| 5.2.7 DDR Close Up on Top Layer            | 46 |

| 5.2.8 DDR Close Up on Bottom Layer         | 47 |

| 5.3 PCB Trace Widths and Clearance          | 48 |

|---------------------------------------------|----|

| Chapter 6. Initial Board Bring-Up Procedure |    |

| 6.1 Introduction                            | 49 |

| Worldwide Sales and Service                 | 52 |

NOTES:

# EVB-LAN9668 EVALUATION BOARD USER'S GUIDE

# Preface

# NOTICE TO CUSTOMERS

All documentation becomes dated, and this manual is no exception. Microchip tools and documentation are constantly evolving to meet customer needs, so some actual dialogs and/or tool descriptions may differ from those in this document. Please refer to our website (www.microchip.com) to obtain the latest documentation available.

Documents are identified with a "DS" number. This number is located on the bottom of each page, in front of the page number. The numbering convention for the DS number is "DSXXXXA", where "XXXXX" is the document number and "A" is the revision level of the document.

For the most up-to-date information on development tools, see the MPLAB<sup>®</sup> IDE online help. Select the Help menu, and then Topics to open a list of available online help files.

# INTRODUCTION

This chapter contains general information that will be useful to know before using the Microchip EVB-LAN9668 Evaluation Board. Items discussed in this chapter include:

- Document Layout

- Conventions Used in this Guide

- The Microchip Website

- Development Systems Customer Change Notification Service

- Customer Support

- Document Revision History

# DOCUMENT LAYOUT

This document features the EVB-LAN9668 Evaluation Board. The manual layout is as follows:

- **Chapter 1. "Overview"** This section provides an overview of the additional documentation needed and a brief description of the Evaluation Board feature list.

- Chapter 2. "Management Software" This section gives a brief introduction of the turnkey managed software, which offers a Cisco-style Command Line Interface, as well as Web-based Graphical User Interface, to set up and control the switch.

- Chapter 3. "Board Details" This section briefly walks through the different connector types and LEDs found on the Evaluation Board.

- Chapter 4. "Hardware Details" This section describes the hardware implementation in details.

- Chapter 5. "PCB Layout" This section shows the different PCB layers, especially the routing to the DDR RAM.

- Chapter 6. "Initial Board Bring-Up Procedure" This section lists the order of milestones to make a complete bring-up of the Evaluation Board.

# **CONVENTIONS USED IN THIS GUIDE**

This manual uses the following documentation conventions:

#### **DOCUMENTATION CONVENTIONS**

| Description Represents                           |                                                                                                              | Examples                                     |  |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| Arial font:                                      | 1                                                                                                            | 1                                            |  |

| Italic characters                                | Referenced books                                                                                             | MPLAB <sup>®</sup> IDE User's Guide          |  |

|                                                  | Emphasized text                                                                                              | is the only compiler                         |  |

| Initial caps                                     | A window                                                                                                     | the Output window                            |  |

|                                                  | A dialog                                                                                                     | the Settings dialog                          |  |

|                                                  | A menu selection                                                                                             | select Enable Programmer                     |  |

| Quotes                                           | A field name in a window or dialog                                                                           | "Save project before build"                  |  |

| Underlined, italic text with right angle bracket | A menu path                                                                                                  | <u>File&gt;Save</u>                          |  |

| Bold characters                                  | A dialog button                                                                                              | Click OK                                     |  |

|                                                  | A tab                                                                                                        | Click the <b>Power</b> tab                   |  |

| N'Rnnnn                                          | A number in verilog format,<br>where N is the total number of<br>digits, R is the radix and n is a<br>digit. | 4'b0010, 2'hF1                               |  |

| Text in angle brackets < >                       | A key on the keyboard                                                                                        | Press <enter>, <f1></f1></enter>             |  |

| Courier New font:                                | - <b>-</b>                                                                                                   | •                                            |  |

| Plain Courier New                                | Sample source code                                                                                           | #define START                                |  |

|                                                  | Filenames                                                                                                    | autoexec.bat                                 |  |

|                                                  | File paths                                                                                                   | c:\mcc18\h                                   |  |

|                                                  | Keywords                                                                                                     | _asm, _endasm, static                        |  |

|                                                  | Command-line options                                                                                         | -Opa+, -Opa-                                 |  |

|                                                  | Bit values                                                                                                   | 0, 1                                         |  |

|                                                  | Constants                                                                                                    | OxFF, `A'                                    |  |

| Italic Courier New                               | A variable argument                                                                                          | file.o, where file can be any valid filename |  |

| Square brackets [ ]                              | Optional arguments                                                                                           | mcc18 [options] file<br>[options]            |  |

| Curly brackets and pipe character: {   }         | Choice of mutually exclusive arguments; an OR selection                                                      | errorlevel {0 1}                             |  |

| Ellipses                                         | Replaces repeated text                                                                                       | <pre>var_name [, var_name]</pre>             |  |

|                                                  | Represents code supplied by<br>user                                                                          | <pre>void main (void) { }</pre>              |  |

#### WARRANTY REGISTRATION

Please complete the enclosed Warranty Registration Card and mail it promptly. Sending the Warranty Registration Card entitles users to receive new product updates. Interim software releases are available at the Microchip website.

#### THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

#### DEVELOPMENT SYSTEMS CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions, or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

The Development Systems product group categories are:

- **Compilers** The latest information on Microchip C compilers, assemblers, linkers and other language tools. These include all MPLABCC compilers; all MPLAB assemblers (including MPASM<sup>™</sup> assembler); all MPLAB linkers (including MPLINK<sup>™</sup> object linker); and all MPLAB librarians (including MPLIB<sup>™</sup> object librarian).

- **Emulators** The latest information on Microchip in-circuit emulators. This includes the MPLAB<sup>®</sup> REAL ICE<sup>™</sup> and MPLAB ICE 2000 in-circuit emulators.

- In-Circuit Debuggers The latest information on the Microchip in-circuit debuggers. This includes MPLAB ICD 3 in-circuit debuggers and PICkit<sup>™</sup> 3 debug express.

- **MPLAB IDE** The latest information on Microchip MPLAB IDE, the Windows<sup>®</sup> Integrated Development Environment for development systems tools. This list is focused on the MPLAB IDE, MPLAB IDE Project Manager, MPLAB Editor and MPLAB SIM simulator, as well as general editing and debugging features.

- Programmers The latest information on Microchip programmers. These include production programmers such as MPLAB REAL ICE in-circuit emulator, MPLAB ICD 3 in-circuit debugger and MPLAB PM3 device programmers. Also included are non-production development programmers such as PICSTART<sup>®</sup> Plus and PICkit<sup>™</sup> 2 and 3.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support

# DOCUMENT REVISION HISTORY

| Revisions                 | Section/Figure/Entry | Correction |

|---------------------------|----------------------|------------|

| DS50003349A<br>(06-23-22) | Initial release      |            |

# EVB-LAN9668 EVALUATION BOARD USER'S GUIDE

# Chapter 1. Overview

# 1.1 INTRODUCTION

This hardware manual describes the design of the LAN9668 reference board, demonstrating the Maserati TSN Ethernet Switch architecture. The LAN9668 reference board is based on the EVB-LAN9668 (Part Number: EV18W53) Reference Design Schematic.

#### 1.1.1 Audience

This document is primarily intended for hardware and software engineers who want to get an overview of designing products based on the LAN9668.

#### 1.1.2 References

#### 1.1.2.1 MICROCHIP DOCUMENTS

- EVB-LAN9668B Reference Design Schematic, 2021/12/09

- LAN9668 Product Data Sheet (www.microchip.com/DS00004031)

- LAN8814 Product Data Sheet (www.microchip.com/DS00003592)

- LAN8814 Errata (www.microchip.com/DS800001002)

- ZL30771\_772\_773 Data Sheet

- ENT-AN1187 Using the Serial GPIO/LED Controller

#### 1.1.2.2 IEEE STANDARDS

- IEEE802.1D, Media Access Control Bridges

- IEEE802.1Q, Virtual Bridged Local Area Networks

- IEEE802.3, CSMA/CD Access Method and Physical Layer Specification

- IEEE1588-2008, Precision Clock Synchronization Protocol

#### 1.1.3 Terms and Abbreviations

- AMS: Automatic Media-Sense

- CLI: Command Line Interface

- EMI: Electromagnetic Interference, emissions

- JTAG: Joint Test Access Group, IEEE1149

- LVDS: Low Voltage Differential Signaling

- LVTTL: Low Voltage TTL

- PCS: Physical Coding Sublayer

- PHY: Physical layer device

- PTP: Precision Time Protocol, IEEE1588

- SI: Serial Interface, SPI

- SME: Small/Medium Enterprise

- SSM: Synchronization Status Message

- SyncE: Synchronous Ethernet, ITU-T G.8262/Y.1362

# 1.2 FEATURES

#### 1.2.1 Feature List

The EVB-LAN9668 evaluation board use case is a Managed TSN Switch, exposing the main interfaces and features of LAN9668.

- LAN9668 TSN Switch with internal 600 MHz ARM<sup>®</sup> Cortex<sup>®</sup> A7 CPU and external 1GB SDRAM

- 8x tri-speed (10/100/1000M) RJ45 front ports using LAN8814 QuadPHY via QSGMII

- · On-board SyncE DPLL ZL30772 to generate all the required clocks

- micro USB 2.0 port for management and debugging through a firmware driven Command Line Interface (CLI)

- PCIe<sup>®</sup> 2.0 End Point interface through USB3 connector or SPI for external CPU control

- Four SMA connectors for SyncE and PTP applications

- Reset button, which can also be used for SW detection of long press for resetting to defaults

- System status LED and per network port status LEDs for link and activity indication

- 2x20 pin Expansion header exposing various interfaces: UART, QSPI, I<sup>2</sup>C, PTP, CAN, and IRQ

- Standard 12V DC power input Jack (5.5 mm/2.5 mm center pin) or 12-48V DC input terminal screw connector type

### 1.2.2 CPU System

# 1.2.2.1 EMBEDDED ARM<sup>®</sup> CORTEX<sup>®</sup> A7 CPU SYSTEM

By default, the LAN9668 switch core is managed by its embedded CPU system with on-board SDRAM and SPI boot from either NOR or e-MMC<sup>™</sup> NAND Flash (or both).

- · Embedded ARM Cortex A7 single core 32-bit processor operating at 600 MHz

- External memories include 1 GB DDR3L SDRAM, 2 MB NOR, and/or 4 GB e-MMC SPI boot Flash memory

The Flash devices are used as device stage boot loader in a Secure boot environment.

#### 1.2.2.2 EXTERNAL CPU CONNECTOR

Optionally, an external host CPU system can be connected to and control the LAN9668 configured as a client device through an external CPU connector, using either:

- PCle 2.0 End Point cabled to an external host system using a non-standard USB3 connector

- SPI serial register access through the switch SI client interface exposed in the Expansion header

#### 1.2.3 Management and User I/O

The embedded CPU system includes that the switch can be locally managed either through a WebGUI or CLI:

- · WebGUI/https through any Ethernet port connected to the switch core

- micro USB 2.0 (or Telnet session) for CLI using a standard terminal application, like PuTTY

#### 1.2.4 CuPHYs

The reference board uses two tri-speed QuadPHYs LAN8814, which have low EMI line drivers with integrated line-side termination resistors, support for HP Auto MDI-/MDI-X<sup>™</sup>, and operate over standard Category 5 cabling at 10/100/1000 Mbit/s and Category 3 cabling at 10 Mbit/s.

#### 1.2.5 Timing and Synchronization

#### 1.2.5.1 SYNCE

The reference board supports SyncE through an on-board Microchip ZL30772 (Redwood) SyncE controller. SyncE is managed as part of the general switch management software.

The DPLL generates two reference clocks to LAN9668. The clock source can be either a free-running oscillator or a clock recovered from one of the CuPHY ports. The two LAN8814 CuPHYs simply daisy-chain the selected recovered clocks (2x) to the ZL30772 input.

For SyncE, the DPLL prioritizes and selects the clock source under software control and attenuates jitter before presenting the resulting clocks to LAN9668 and the two LAN8814. There is also one input and one output SMA available for SyncE, supporting 10 MHz, 2.048 MHz, and 1.544 MHz input and output station clocks.

#### 1.2.5.2 PTP/IEEE1588V2

Precision Time Protocol (PTP) interfacing is available through all network ports (with high accuracy timestamping in the LAN8814 CuPHYs) and through input and output of 1 PPS SMA connectors.

The LAN9668 can be configured as boundary clock, transparent clock, PTP master, or PTP slave. LAN9668 can support both one-step and two-step operations.

A free-running 114.285 MHz XO provides the base clock to the board DPLL. Optionally, a 25 MHz TCXO can be used to provide improved frequency stability.

NOTES:

# EVB-LAN9668 EVALUATION BOARD USER'S GUIDE

# **Chapter 2. Management Software**

# 2.1 INTRODUCTION

The reference board can be managed remotely by using a browser-based graphical user interface (WebGUI) or locally through an USB serial port using a command line interface (CLI). The reference board is intended to run with one of the WebStaX turnkey programs VSC6816-VSC6819. (It is, however, also possible to use the small demo application found in the API (MESA).)

# 2.2 CLI FOR MANAGEMENT AND DEBUGGING

The board can be connected directly to a PC USB port using a basic USB 2.0 A-Male to micro-B cable to access the CLI.

When connected, the PC will detect the LAN9668 built-in USB controller. There is no need to set up baud rate, data bits, parity or flow control in the terminal program running on the PC, as it is standard USB to USB 2.0 connection. However, in case the terminal program needs this, the COM port can be set up to run 8 data bits, 1 stop bit, no parity, 115200 baud, and without flow control.

Login into the switch can be made by using the default username, *admin* (without quotes). The default password is blank (that is, field value is empty). Help screens are available through the "?" or "help" commands.

A general way to restore default settings and password is to make a loop between port 1 and 2 during power-on (or simply press and hold the **Reset** button) and wait for the Switch Application to complete its boot-up.

```

💻 COM12 - Tera Term VT

File Edit Setup Control Window Help

Press ENTER to get started

Username: admin

Password:

# terminal length 0

# terminal exec-timeout 0

# show interface * status

Speed Aneq

Link Operational Warnings

Interface Mode

----- ------

Gi 1/1 Enabled Auto Yes 1Gfdx

Gi 1/2 Enabled Auto Yes Down

Enabled Auto Yes

Enabled Auto Yes

1Gfdx

1Gfdx

Gi 1/3

IGfdx

IGfdx

IGfdx

IGfdx

IGfdx

Inabled Auto Yes

IGfdx

Enabled Auto Yes

IGfdx

Enabled Auto Yes

IGfdx

ICfdx

ICf

Gi 1/4

Gi 1/5 Enabled Auto Yes

Gi 1/6

Gi 1/7

Gi 1/8

# show interface vlan 1

VLAN 1

LINK: 02-00-c1-bf-15-7c Mtu:1500 <UP BROADCAST MULTICAST>

IPv4: 10.205.28.57/24 10.205.28.255

IPv6: fe80::c1ff:febf:157c/64 <>

DHCP: State: BOUND server: 10.205.28.9

# configure terminal

(config) # aggregation mode dmac smac ip

(config) # interface GigabitEthernet 1/1-4

(config-if)# aggregation group 1 mode ?

active Active LACP

on

Static aggregation

passive Passive LACP

<cr>

(config-if) # aggregation group 1 mode on

(config-if) # end

# show interface GigabitEthernet 1/1-4 statistics packets

Interface

Rx Packets Tx Packets

_____

GigabitEthernet 1/1

GigabitEthernet 1/2

1092

0

244

0

GigabitEthernet 1/3 66

GigabitEthernet 1/4 258

258

66

# show spanning-tree gi

```

#### FIGURE 2-1: CLI SCREENSHOT EXAMPLE

One important use of the CLI is to determine the IP address of the switch, if DHCP is enabled. This is done through the show interface vlan 1 command. The command displays the IP address that the WebGUI is available on.

An example of the CLI output when setting up Static Aggregation on four 1G ports is shown in Figure 2-1.

#### 2.3 WEBGUI FOR MANAGEMENT

The WebStaX turnkey programs VSC6816-VSC6819 offers WebGUI access to manage the switch setup and to get current status.

The WebGUI is available from, for example, a PC connected to a network port. Ensure that the PC and switch are on the same subnet.

Start the PC's browser, point the browser at the switch's IP address (default static IP address is 192.0.2.1), and enter the login credentials when prompted. Default username is *admin*, and the default password is blank (that is, field value is empty). A graphical representation of the switch ports will appear. Setup is done by selecting the configuration menu at the top left and selecting an appropriate submenu. Likewise, the status can be displayed through the Monitor menu. New versions of the Switch Application can be uploaded through the Maintenance menu. Help screens are available through the "?" button at the top right. Figure 2-2 shows the Port 1 RMON statistics.

| 🐼 IStaX                                         | × +                                  |                    |                                      | ~ -                   |              |

|-------------------------------------------------|--------------------------------------|--------------------|--------------------------------------|-----------------------|--------------|

| ← → C ▲ No                                      | ot secure   10.205.28.57/index.htm   |                    |                                      | 🖻 🖈 💽 🕯               | • 📧 E        |

| WebStaX [Jenkins]                               | 🔇 WebHome < Main 📙 Confluence        | Salesforce . Perfo | rce 📙 PCle 📃 Microse                 | mi » 🛅                | Reading list |

|                                                 |                                      |                    |                                      |                       |              |

| 🕥 Міскосн                                       | 1IP                                  | IStaX™ GigaB       | it Ethernet Swite                    | sh 🗳                  | • 🗭 🚱        |

| Configuration<br>Monitor                        | Detailed Port Statistics Port 1      |                    | Port 1 🗸 Au                          | uto-refresh 🗌 Refresh | Clear        |

| System                                          | Receive Tota                         |                    | Transm                               | it Total              |              |

| Green Ethernet                                  | Rx Packets                           | 1905               | Tx Packets                           | 286                   | i .          |

| ✓ Ports<br>■ State                              | Rx Octets                            | 246359             | Tx Octets                            | 39535                 |              |

| <ul> <li>Traffic Overview</li> </ul>            | Rx Unicast                           |                    | Tx Unicast                           | 0                     |              |

| <ul> <li>QoS Statistics</li> </ul>              | Rx Multicast                         |                    | Tx Multicast                         | 282                   |              |

| <ul> <li>QCL Status</li> </ul>                  | Rx Broadcast                         |                    | Tx Broadcast                         | 4                     |              |

| <ul> <li>Detailed Statistics</li> </ul>         | Rx Pause                             | 0                  |                                      | 0                     |              |

| <ul> <li>Name Map</li> </ul>                    | Receive Size Cou                     |                    | Transmit Siz                         |                       |              |

| ▶ CFM                                           | Rx 64 Bytes                          |                    | Tx 64 Bytes                          | 6                     |              |

| • APS                                           | Rx 65-127 Bytes                      |                    | Tx 65-127 Bytes                      | 172                   |              |

| ERPS                                            | Rx 128-255 Bytes<br>Rx 256-511 Bytes |                    | Tx 128-255 Bytes<br>Tx 256-511 Bytes | 103                   |              |

| <ul> <li>Media Redunancy</li> </ul>             | Rx 512-1023 Bytes                    | 05                 | Tx 512-1023 Bytes                    | 5                     |              |

| Link OAM                                        | Rx 1024-1526 Bytes                   | 0                  | Tx 1024-1526 Bytes                   | 0                     |              |

| DHCPv4                                          | Rx 1527- Bytes                       | ő                  |                                      | Ő                     |              |

| ► DHCPv6                                        | Receive Queue Co                     |                    | Transmit Que                         |                       |              |

| <ul> <li>Security</li> </ul>                    | Rx Q0                                |                    | Tx Q0                                | 40                    |              |

| <ul> <li>Aggregation</li> <li>Status</li> </ul> | Rx Q1                                |                    | Tx Q1                                | 0                     |              |

| LACP                                            | Rx Q2                                | Ō                  | Tx Q2                                | õ                     |              |

| <ul> <li>Loop Protection</li> </ul>             | Rx Q3                                | 0                  | Tx Q3                                | 0                     |              |

| Spanning Tree                                   | Rx Q4                                | 0                  | Tx Q4                                | 0                     |              |

| ► MVR                                           | Rx Q5                                | 0                  | Tx Q5                                | 0                     |              |

| ▶ IPMC                                          | Rx Q6                                |                    | Tx Q6                                | 0                     |              |

| ► LLDP                                          | Rx Q7                                | 0                  |                                      | 246                   |              |

| ▶ PTP                                           | Receive Error Cou                    |                    | Transmit Err                         |                       |              |

| <ul> <li>MAC Table</li> </ul>                   | Rx Drops                             |                    | Tx Drops                             | 0                     |              |

| ▶ VI ANS                                        | Rx CRC/Alignment                     | 0                  | Tx Late/Exc. Coll.                   | 0                     |              |

| • MVRP                                          | Rx Undersize<br>Rx Oversize          | 0                  |                                      |                       |              |

| <ul> <li>sFlow</li> </ul>                       |                                      | 0                  |                                      |                       |              |

| ▶ DDMI                                          | Rx Fragments<br>Rx Jabber            | 0                  |                                      |                       |              |

| UDLD                                            | Rx Filtered                          | 1842               |                                      |                       |              |

| ▶ TSN                                           | Receive MM Cour                      |                    | Transmit M                           | A Counters            |              |

| ▶ OSPF                                          | Rx MM Fragments                      | 0                  | Tx MM Fragments                      | o counters            |              |

| ♦ OSPFv3                                        | Rx MM Assembly Ok                    | 0                  | Tx MM Hold                           | 0                     |              |

| ▶ RIP                                           | Rx MM Assembly Errors                | 0                  |                                      | U                     |              |

| Diagnostics                                     | Rx MM SMD Errors                     | ő                  |                                      |                       | -            |

#### FIGURE 2-2: WEBGUI SCREENSHOT EXAMPLE

NOTES:

# EVB-LAN9668 EVALUATION BOARD USER'S GUIDE

# **Chapter 3. Board Details**

# 3.1 EVB-LAN9668 REFERENCE BOARD

#### 3.1.1 Board Overview

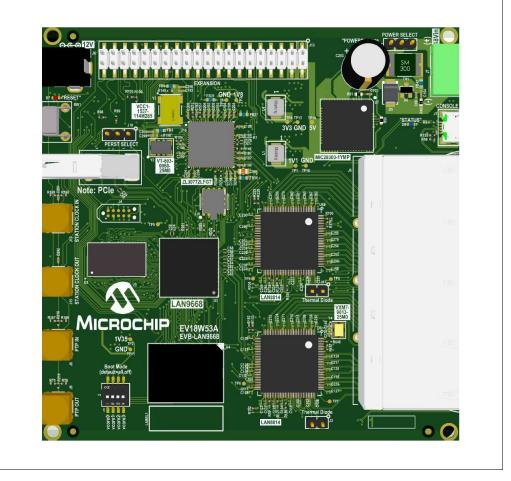

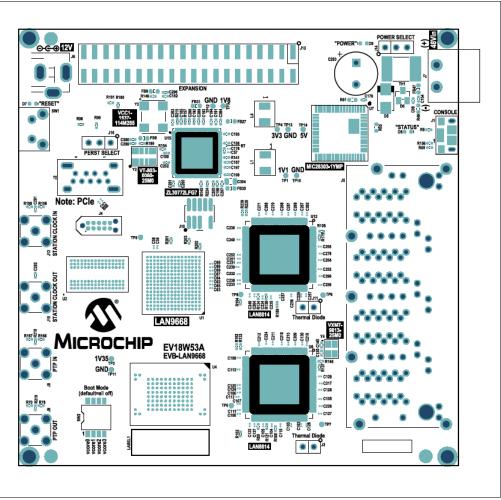

Figure 3-1 shows the component placement on the EVB-LAN9668B PCB.

#### FIGURE 3-1: EVB-LAN9668 REFERENCE BOARD

#### 3.1.2 Power DC Input and LED

The reference board is powered through either a standard 12VDC/1.5A PSU or through 12V-48VDC PSU. Pin strapping is used (J14) to select between the two power sources going to an on-board 5V, 3.0A power module. The power module then supplies different local DC/DC converters.

A single green LED (D9) indicates power-on using the 3.3V supply.

### 3.1.3 Reset Button and LED

A reset button is available on the reference board. When pressed, it drives the input of the voltage supervisor low, and thus creating a hard reset to the board. A red LED (D7) is used for indication.

If the reset button is held, reset is released. The state of the reset button can be read by software once it is running again to determine long press and configuring the board back to the default setup.

### 3.1.4 System Status LED

A blue LED (D8) shows the system status. It is controlled by software and is off during board reset.

#### 3.1.5 Front Port Layout and LEDs

Software mapping is used to compensate for the physical board routing of PHY ports to the front ports together with their MIIM addresses.

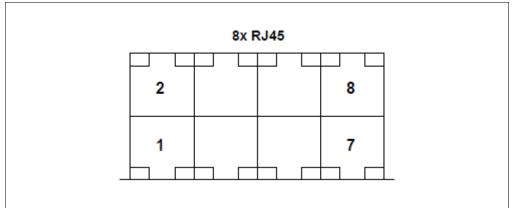

Figure 3-2 shows the software mapping result to the front port layout on the EVB-LAN9668B PCB.

FIGURE 3-2: FRONT PORT LAYOUT ON EVB-LAN9668B

Two LEDs (green/yellow) are available on each RJ45 slot in the magnetic jack. The port status LEDs are automatically controlled by the LAN8814. The left LED signals 1G link/traffic (green solid/blinks) and the right LED signals 10/100M link/traffic (yellow solid/blinks).

#### 3.1.6 Rear SMA Connectors

There are four SMA connectors, of which two are used as inputs and two as outputs.

One of the SMA input connectors is available for 1PPS into the LAN9668 PTP0 and optional to the board DPLL and Expansion header. The other SMA input (Station Clock Input) is for various frequencies (for example, 1.544 MHz, 2.048 MHz, and 10 MHz) into the board DPLL.

**Note:** The SMA inputs are LVTTL and are 3V3-tolerant (not 5V-tolerant). The Station Clock Input is AC-coupled.

One of the SMA output connectors is used for 1PPS from the LAN9668. Optionally, it can be driven by the board DPLL. The other SMA output (Station Clock Output) is for various frequencies (for example, 1.544 MHz, 2.048 MHz, and 10 MHz) from the board DPLL. The 1PPS output uses LVTTL levels, and the Station Clock Output uses LVTTL levels and is AC-coupled.

#### 3.1.7 USB 2.0 Serial Port

The reference board can be controlled through a standard serial micro-USB 2.0 port using CLI commands from a terminal application, like PuTTY or TeraTerm.

# 3.1.8 PCle<sup>®</sup> 2.0 End Point

The reference board offers a standard PCIe 2.0 End Point through a non-standard USB3 type of connection. It can be used together with the PCE2PCE-N07 adapter from the PCE164P-N07 kit.

# 3.1.9 ARM<sup>®</sup> CPU JTAG Connector

The reference board offers a standard 10-pin (0.05") ARM CPU JTAG header to be used for boundary scan and In-Circuit Emulator (ICE). ICE can be used for debugging functions, such as downloading code and single-stepping through programs.

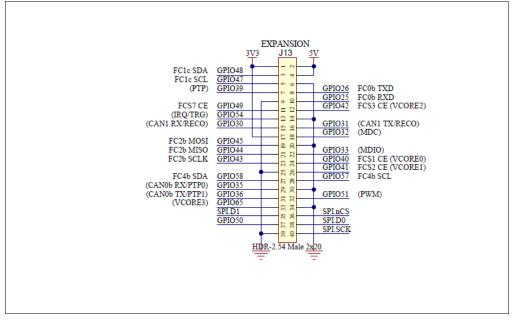

#### 3.1.10 Expansion Header

The Expansion header is targeting Raspberry PI compatibility. It is a 2x10, 0.1" pin header. It can also be used for programming the on-board NOR Flash device, can give an external CPU control over the SPI client register access interface, and can expose various GPIO signals being in Alternate mode:

| • UART:  | RXD, TXD                               | (FLEXCOM 0, mode B) |

|----------|----------------------------------------|---------------------|

| • I2C:   | SCL, SDA                               | (FLEXCOM 1, mode C) |

| • I2C:   | SCL, SDA                               | (FLEXCOM 4, mode B) |

| • SPI:   | SCLK, MISO, MOSI + 5/6 Flex_Shared nCS | (FLEXCOM 2, mode B) |

| • QSPI0: | SPI.SCK, SPI.D1, SPI.D0 and SPI.nCS    | (NOR Flash/LAN9668) |

|          |                                        |                     |

The remaining Expansion header GPIO signals can function as normal GPIO pins when using default software settings. However, they can also be enabled with LAN9668-specific functionality, which is not found in the original Raspberry PI header.

- CAN0: RX, TX

- CAN1: RX, TX or Recovered clock 0/1

- MIIM (mode B enabling MIIM in mode B will disable mode A to the LAN8814)

- IRQ or TRG

- PWM

- PTP

Likewise, the on-board Boot mode strapping, VCORE\_CFG[3:0], can be overruled through the Expansion header.

#### 3.1.11 Boot Modes and Reference Clock

The LAN9668 Boot mode can be selected through a 4-pin DIP switch. The system is default '0001' set to boot from the serial NOR Flash device. Additionally, it is possible to strap the switch core and SerDes/PHY reference clock mode and frequency through strapping pins using resistors. The default setup is 25 MHz core clock and 125 MHz SerDes/PHY clock.

NOTES:

# EVB-LAN9668 EVALUATION BOARD USER'S GUIDE

# **Chapter 4. Hardware Details**

# 4.1 BLOCK DIAGRAMS

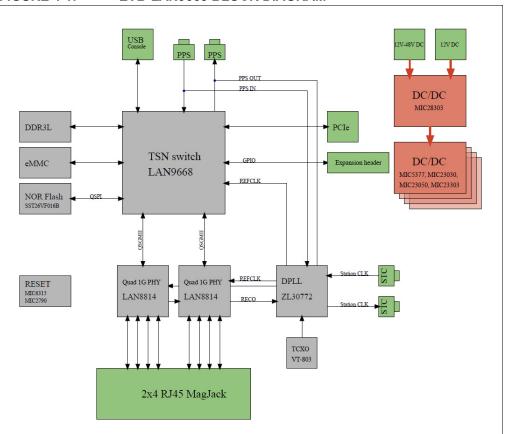

Figure 4-1 illustrates the block diagram of the reference board with its eight copper front ports and on-board DPLL.

FIGURE 4-1: EVB-LAN9668 BLOCK DIAGRAM

The design is based on the LAN9668 TSN switch, which includes a single core ARM Cortex A7 CPU that externally connects to 1 GB SDRAM, 4 GB e-MMC, and 2 MB NOR Flash memories — both can be used as second stage bootloader in a Secure Boot environment. The larger e-MMC memory is also used for bulk storage.

Optionally, an external CPU system can be connected and control the switch through a PCIe 2.0 End Point interfaces and/or through an SPI client interface found in the Expansion header.

A SyncE-capable DPLL ZL30772 generates all required reference clocks. The clock source can be either a free-running oscillator (XO) or a recovered clock from one of the CuPHY ports on the two LAN8814. The selected recovered clocks are daisy-chained through the two LAN8814 to the DPLL.

The DPLL jitter attenuates the selected source clock and provides as reference clock to the LAN9668 switch and the two LAN8814 QuadPHYs. The generated clocks can be sourced individually to make two independent clock domains: one domain for SyncE and one domain for IEEE 1588.

There are four SMA connectors, which can be used for SyncE and IEEE 1588 applications.

Local management and software debugging can be made through the LAN9668 built-in USB 2.0 port.

# 4.2 LAN9668 VCORE CPU SYSTEM

By default, the LAN9668 switch core is managed by its embedded CPU system with on-board SDRAM.

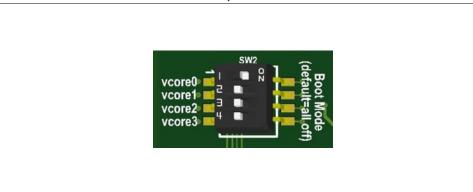

#### 4.2.1 Boot Mode Strapping

LAN9668 uses strapping pins to select the initial boot mode. These pins are named VCORE\_CFG[3:0] and located on GPIO[65, 42:40]. A four-pin DIP switch, SW2, is used to make the actual strapping.

#### FIGURE 4-2: 4-PIN DIP SWITCH, SW2

When SW2 is set to '0001', the embedded CPU uses the QSPI boot interface connected to a NOR Flash device, as second bootloader in a Secure Boot environment. Setting SW2 to '0000', the e-MMC is being used. Both settings require the Flash device to be pre-/programmed with a suitable bootloader.

The NOR Flash device can be programmed through the Expansion header using a Flash device programmer. Therefore, for production reasons, using the NOR Flash device is the board's default setup.

| TABLE 4-1: BC | OOT MODES |

|---------------|-----------|

|---------------|-----------|

| SW2  | VCORE_CFG[3:0] Description                                                        |  |

|------|-----------------------------------------------------------------------------------|--|

| 0000 | Boot from e-MMC. Boot traces on FLEXCOM3 mode B.                                  |  |

| 0001 | Boot from QSPI0. Boot traces on FLEXCOM3 mode B. (Default)                        |  |

| 0110 | PCIe 2.0 End Point. Internal CPU is disabled.                                     |  |

| 1111 | QSPI0/SI client and MIIM client interfaces are enabled. Internal CPU is disabled. |  |

Using an external CPU, SW2 can be set to either '0110' to enable the PCIe 2.0 End Point controller found on the USB3 female connector, or to '1111' for register access through the SPI client or MIIM client interfaces, which are both found in the Expansion header.

#### 4.2.2 PLL Strapping

LAN9668 PLL strapping, PLL\_STRP[1,0] located on GPIO[36,27], is set to have 25 MHz on switch core (and internal CuPHYs — not used in this design) and 125 MHz to the SerDes.

The same 125 MHz clock source is distributed to each of the LAN8814 QuadPHYs. Thus, the DPLL generated 125 MHz supports SyncE on the Ethernet ports and the 25 MHz supports IEEE 1588 timing domain in the switch core for its PTP engines.

TABLE 4-2: PLL STRAPPING MODES

| Pulls | PLL_STRP[1:0] Description                 |  |

|-------|-------------------------------------------|--|

| 00    | SerDes: 25 MHz, Cu PHY: 25 MHz            |  |

| 01    | SerDes: 125 MHz, Cu PHY: 125 MHz          |  |

| 10    | SerDes: 125 MHz, Cu PHY: 25 MHz (default) |  |

| 11    | Reserved                                  |  |

Optionally, the board is prepared to use a local 25 MHz XTAL as reference input instead of the DPLL.

#### 4.2.3 DDR3L SDRAM

The LAN9668 SDRAM interface is 16 bits wide and is targeted to operate at a clock rate of 600 MHz, requiring an SDRAM of speed grade 1200 MT/s or better.

The reference board is equipped with one 800 MHz 1 GB DDR3L SDRAM (x16) and has been tested up to 1325 MT/s. Lower densities can be substituted depending on the application. The minimum is 128 MB.

The reference design uses resistor dividers to generate the DDR\_VRE, instead of using a dedicated DDR Power Manager device, like the MIC5166YML, as there is no need for driving DDR termination. DDR termination resistors can be avoided when keeping the maximum trace length below 35 mm.

#### 4.2.4 SPI NOR Flash Device

The reference board is equipped with a 2 MB NOR QSPI boot Flash device (8-pin SOIC), which is solely intended to hold a second stage bootloader in a Secure Boot environment. The NOR Flash device can be removed if using e-MMC or SD Card for boot-up.

#### 4.2.5 SPI NOR Flash Programming

The NOR Flash device can be programmed using an external Flash programmer connected to the pins in the Expansion header. This includes a reset signal through pin header J16.2, on which the programmer can keep the LAN9668 in reset, so it will not drive the SI\_CLK and SI\_DO outputs while programming the SPI Flash device. Alternatively, the LAN9668 can be set into SPI Client mode '1111' using the SW2, DIP switch.

To connect the Universal Programmer from ASIX (Forte or Presto), see Table 4-3.

Expansion HeaderUniversal Programmer from ASIXPin 1 (VccSPI)P3 (VDD) (Red)Pin 35 (SI.D1)P7 (DO/I) (White)Pin 36 (SPI.nCS0)P1 (P) (Yellow)

TABLE 4-3: PROGRAMMING SIGNALS

| Expansion Header | Universal Programmer from ASIX |  |

|------------------|--------------------------------|--|

| Pin 38 (SI.D0)   | P5 (DI/D) (White)              |  |

| Pin 39 (GND)     | P4 (GND) (Blue)                |  |

| Pin 40 (SI.CLK)  | P6 (C) (Green)                 |  |

#### TABLE 4-3: PROGRAMMING SIGNALS (CONTINUED)

#### 4.2.6 e-MMC<sup>™</sup> Flash Device, Bulk Storage

The reference board is equipped with a 4 GB e-MMC for bulk storage.

Alternatively, it can be used as a second stage boot ROM instead of the NOR Flash device, and thus avoids having the NOR Flash device mounted. For production, it is then recommended to use a preprogrammed e-MMC device, or to have an additional test connector, like TC2050, placed between LAN9668 and the e-MMC for on-board programming. FLEXCOM 3 mode B can also be used for programming the e-MMC.

**Note:** This has not yet been validated as the current design uses FLEXCOM3 in mode A.

#### 4.2.7 PHY Interrupts

A dedicated PHY interrupt input signal, MIIM\_INT#, is connected to the LAN9668 GPIO 24/IRQ\_IN\_5C. The MIIM\_INT# is a shared (open collector) interrupt from the two LAN8814 QuadPHYs. Hence, when an interrupt occurs, software must poll the possible sources for the current interrupt status through their respective MIIM interface, because it is not possible to distinguish which PHY source has activated the shared interrupt signal.

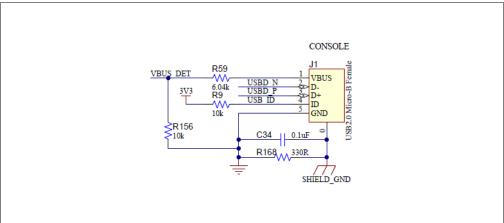

#### 4.2.8 Micro USB Serial Port

In the LAN9668, the USB device and host interface share the same internal UTMI transceiver, and the same data pins, USBD\_P and USBD\_N. The interface supports up to 480 MHz USB 2.0 high-speed transmission speed.

On the reference board, the USB port, J1, is configured in Device mode and is used as the console port.

FIGURE 4-3: USB DEVICE MODE CONNECTION

VBUS\_DET is divided by a resistor network to reduce the voltage from 5.0V to 3.125V and connects to GPIO\_8, which has the overlaid function of VBUS detection. When GPIO\_8 detects the VBUS, an interrupt can be generated, thus software can enable the USB transceiver. The USB ID from the USB connector is connected to GPIO\_9 to enable the reference board to change between being a USB device and being an initiator (host).

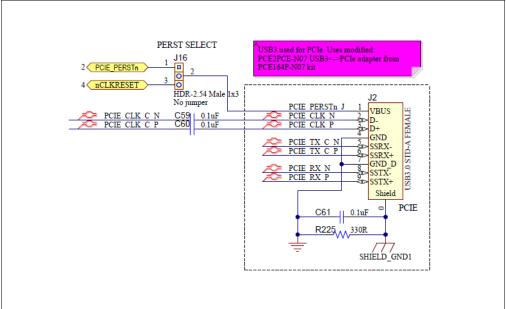

# 4.2.9 PCle<sup>®</sup> 2.0 End Point

LAN9668 implements a single-lane PCIe Gen2 End Point controller, that can be hooked up to any PCIe-capable system. The PCIe client interface can be used by an external CPU to read or write switch registers.

The reference board offers the PCIe 2.0 client through a non-standard USB3 type of connection. It can be used together with the PCE2PCE-N07 adapter from the PCE164P-N07 kit.

FIGURE 4-4: PCIE<sup>®</sup> CLIENT INTERFACE USING USB3 FEMALE CONNECTOR

**Note:** The switch TX direction has AC coupling. It is expected that the PCIe host has similar setup. Likewise, the received PCIe\_CLK is AC-coupled with on-board biasing to VPTX/2.

Optionally, an external reset signal can be routed to LAN9668 — either as PERST# signal or nCLKRESET by using J16. Using the later may not comply to the PCIe reset timing.

**Note:** The LAN9668 has some frame-DMA capabilities, but the injection and extraction rates highly depend on the frame size as the major overhead is in setting up the DMA. The rule of thumb is that injection from the CPU queues is twice as fast as extraction to the CPU queues when using the internal CPU system. A powerful external CPU system can however easily make it opposite and much faster.

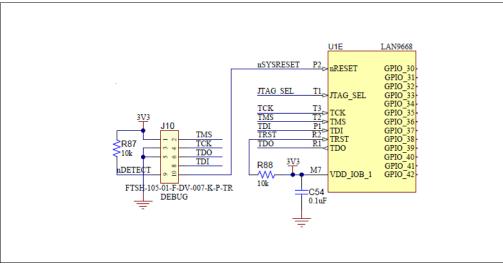

# 4.2.10 ARM<sup>®</sup> CPU JTAG Connector

The reference board offers a standard 10-pin (0.05") ARM CPU JTAG header, J10, to be used for boundary scan and In-Circuit Emulator (ICE). ICE can be used for debugging functions, such as downloading code and single-stepping through programs.

#### FIGURE 4-5:

JTAG INTERFACE

TABLE 4-4:JTAG HEADER, J10

| Pin | JTAG      | In/Out   | Remarks                |

|-----|-----------|----------|------------------------|

| 1   | 3.3V      | —        | Power                  |

| 2   | TMS       | VIS (PU) | Test mode select input |

| 3   | GND       | —        | Ground                 |

| 4   | ТСК       | VIS (PU) | Test clock input       |

| 5   | GND       | —        | Ground                 |

| 6   | TDO       | VO (PU)  | Test data output       |

| 7   | —         | —        | NC                     |

| 8   | TDI       | VIS (PU) | Test data input        |

| 9   | nDETECT   | VIS (PU) | Voltage sense          |

| 10  | nSYSRESET | VIS (PU) | HW reset               |

**Note:** The JTAG signals are not 5V-tolerant. JTAG signal levels are determined by the VDD\_IOB power supply pin, and can be 1.8V, 2.5V, or 3.3V.

The JTAG\_SEL input pin controls the mapping of the chip-level JTAG to select between the CPU subsystem TAP controller or the Test TAP controller. The default resistor setting is pull-up for CPU.

#### 4.2.11 Expansion Header

The Expansion header, J13, is targeting Raspberry Pi compatibility. It is a 2x10, 0.1" pin header. It can also be used for programming the on-board NOR Flash device, give an external CPU control over the SPI client register access interface, and expose various LAN9668 GPIO signals in Alternate mode.

FIGURE 4-6: EXPANSION HEADER LAYOUT, J13

**Note:** An add-on board using the Expansion header *must* have its own Power-On-Reset (POR), and ensure that the VCORE\_CFG strap settings are not overridden unintentionally (GPIO 36, 40, 41, 42, and 65).

The I/O functionality, which is not compatible with Raspberry Pi is marked yellow in Table 4-5. For these, the GPIO signals function as normal GPIO pins when using default software settings.

| Pin | Signal  | Description                               |  |

|-----|---------|-------------------------------------------|--|

| 1   | 3V3     | VccSPI                                    |  |

| 2   | 5V      | —                                         |  |

| 3   | GPIO 48 | I <sup>2</sup> C SDA (FLEXCOM 1C)         |  |

| 4   | 5V      | —                                         |  |

| 5   | GPIO 47 | I <sup>2</sup> C SCL (FLEXCOM 1C)         |  |

| 6   | GND     | —                                         |  |

| 7   | GPIO 39 | (PTP0 IN)                                 |  |

| 8   | GPIO 26 | UART TX (FLEXCOM 0B)                      |  |

| 9   | GND     | —                                         |  |

| 10  | GPIO 25 | UART RX (FLEXCOM 0B)                      |  |

| 11  | GPIO 49 | CE (FLEXCOM shared 7)                     |  |

| 12  | GPIO 42 | CE (FLEXCOM shared 3) (VCORE_CFG2 strap.) |  |

| 13  | GPIO 54 | (IRQ or TRG)                              |  |

| 14  | GND     | _                                         |  |

| 15  | GPIO 30 | (CAN1 RX or Recovered clock 0)            |  |

| 16  | GPIO 31 | (CAN1 TX or Recovered clock 1)            |  |

| 17  | 3V3     |                                           |  |

| 18  | GPIO 32 | (MDC_B)                                   |  |

TABLE 4-5:EXPANSION HEADER — PIN DESCRIPTION

| TABLE 4-5: | EXPANSION HEADER — PIN DESCRIPTION (CONTINUED) |                                                           |  |

|------------|------------------------------------------------|-----------------------------------------------------------|--|

| Pin        | Signal                                         | Description                                               |  |

| 19         | GPIO 45                                        | MOSI (FLEXCOM 2B)                                         |  |

| 20         | GND                                            | —                                                         |  |

| 21         | GPIO 44                                        | MISO (FLEXCOM 2B)                                         |  |

| 22         | GPIO 33                                        | (MDIO_B) When enabling mode B, mode A should be disabled. |  |

| 23         | GPIO 43                                        | SCLK (FLEXCOM 2B)                                         |  |

| 24         | GPIO 40                                        | CE (FLEXCOM shared 1) (VCORE_CFG0 strap)                  |  |

| 25         | GND                                            | —                                                         |  |

| 26         | GPIO 41                                        | CE (FLEXCOM shared 2) (VCORE_CFG1 strap)                  |  |

| 27         | GPIO 58                                        | I <sup>2</sup> C SDA (FLEXCOM 4B)                         |  |

| 28         | GPIO 57                                        | I <sup>2</sup> C SCL (FLEXCOM 4B)                         |  |

| 29         | GPIO 35                                        | (CAN0b RX/PTP0 IN)                                        |  |

| 30         | GND                                            | _                                                         |  |

| 31         | GPIO 36                                        | (CAN0b TX/PTP1 OUT) (PLL_STRP1 strap)                     |  |

| 32         | GPIO 51                                        | (PWM_B)                                                   |  |

| 33         | GPIO 65                                        | (VCORE_CFG3 strap)                                        |  |

| 34         | GND                                            | —                                                         |  |

| 35         | SPI.D1                                         | SPI.D1                                                    |  |

| 36         | SPI.nCS0                                       | SPI.nCS0                                                  |  |

| 37         | GPIO 50                                        | Must be an input. Chip select to LAN9668 and/or NOR Flash |  |

| 38         | SPI.D0                                         | SPI.D0                                                    |  |

| 39         | GND                                            | —                                                         |  |

| 40         | SPI.CLK                                        | SPI.CLK                                                   |  |

|            |                                                |                                                           |  |

### TABLE 4-5: EXPANSION HEADER — PIN DESCRIPTION (CONTINUED)

#### 4.2.12 GPIO Overview Usage

Each GPIO pin in LAN9668 can be assigned to one of up to eight functions. Table 4-6 shows which GPIOs and functionality have been used in the EVB-LAN9668 design. Yellow indicates strapping pins.

|        |             | _        |           |             |                 |

|--------|-------------|----------|-----------|-------------|-----------------|

| GPIO   | Index/Strap | Overlaid | Interface | Exp. Header | Remark          |

| GPI08  | В           | ALT4     | VBUS_DET  | _           | USB VBUS detect |

| GPIO9  | —           | _        | —         | _           | USB_ID          |

| GPIO17 | A           | ALT1     | FLEX3_SCK | _           | DPLL SPI.       |

| GPIO18 | A           | ALT1     | FLEX3_RXD | _           | DPLL SPI.       |

| GPIO19 | A           | ALT1     | FLEX3_TXD | _           | DPLL SPI.       |

| GPIO24 | С           | ALT5     | IRQ_IN    | _           | PHY MIIM_INTn   |

| GPIO25 | В           | ALT1     | FLEX0_RXD | х           | UART RX         |

| GPIO26 | В           | ALT1     | FLEX0_TXD | х           | UART TX         |

| GPIO27 | PLL_STRP0   | _        | _         | _           | _               |

| GPIO28 | A           | ALT1     | MDC       | _           | PHY MIIM        |

| GPIO29 | A           | ALT1     | MDIO      | _           | PHY MIIM        |

| GPIO30 | —           | ALT2     | CANRX1    | х           | (CANRX1/RC0)    |

| GPIO31 | —           | ALT2     | CANTX1    | x           | (CANTX1/RC1)    |

| GPIO32 | В           | ALT6     | MDC       | x           | (MDC)           |

| TABLE 4-6: | GPIO USAGE |

|------------|------------|

|            |            |

| ABLE 4-6: | GPIO USAGE (CONTINUED) |          |                     |             |                       |

|-----------|------------------------|----------|---------------------|-------------|-----------------------|

| GPIO      | Index/Strap            | Overlaid | Interface           | Exp. Header | Remark                |

| GPIO33    | В                      | ALT6     | MDIO                | x           | (MDIO)                |

| GPIO35    | В                      | ALT4     | PTPSYNC_0           | х           | (PTP0 IN/CAN-<br>RX0) |

| GPIO36    | PLL_STRP1              | ALT4     | PTPSYNC_1           | x           | (PTP1<br>OUT/CANTX0)  |

| GPIO37    | JTAG_STRP0             | _        | PTPSYNC_2           | _           | _                     |

| GPIO38    | JTAG_STRP1             | —        | PTPSYNC_3           | —           | PTP3 OUT SM           |

| GPIO39    | —                      | _        | PTPSYNC_4           | х           | (PTP0 IN DPLL         |

| GPIO40    | VCORE_CFG0             | ALT1     | FLEX-<br>_SHARED_1  | х           | CE                    |

| GPIO41    | VCORE_CFG1             | ALT1     | FLEX-<br>_SHARED_2  | х           | CE                    |

| GPIO42    | VCORE_CFG2             | ALT1     | FLEX-<br>_SHARED_3  | х           | CE                    |

| GPIO43    | В                      | ALT1     | FLEX2_SCK           | х           | SCLK                  |

| GPIO44    | В                      | ALT1     | FLEX2_RXD           | х           | MISO                  |

| GPIO45    | В                      | ALT1     | FLEX2_TXD           | х           | MOSI                  |

| GPIO46    | _                      | ALT5     | FLEX-<br>_SHARED_4  | _           | DPLL<br>SPI_CK.CSn    |

| GPIO47    | С                      | ALT1     | FLEX1_RXD           | х           | I2C SCL               |

| GPIO48    | С                      | ALT1     | FLEX1_TXD           | х           | I2C SDA               |

| GPIO49    | _                      | ALT1     | FLEX-<br>_SHARED_7  | x           | CE                    |

| GPIO50    | _                      | ALT1     | FLEX-<br>_SHARED_16 | x           | (GPIO50/nCS)          |

| GPIO51    | В                      | ALT5     | PWM                 | х           | (PWM)                 |

| GPIO52    | В                      | ALT6     | IRQ_IN1             | _           | DPLL nCK_Vali         |

| GPIO53    | -                      | _        | —                   | _           | nPHYRESET             |

| GPIO54    | —                      | ALT2-6   | IRQ3                | х           | (IRQ or TRG)          |

| GPIO55    | —                      | —        | —                   | —           | nBUTTON               |

| GPIO56    | —                      | —        | —                   | —           | nMR                   |

| GPIO57    | В                      | ALT1     | FLEX4_RXD           | х           | I2C SCL               |

| GPIO58    | В                      | ALT1     | FLEX4_TXD           | х           | I2C SDA               |

| GPIO60    | _                      | _        | —                   | —           | COMA                  |

| GPIO61    | С                      | ALT2     | PCle PERST#         | _           | PCIE_PERSTr           |

| GPIO62    | _                      | _        | —                   | _           | CPU_ACT               |

| GPIO65    | VCORE_CFG3             | _        | _                   | х           | _                     |

TABLE 4-6: GPIO USAGE (CONTINUED)

#### TABLE 4-7: GPIO USAGE - EMMC INTERFACE

| GPIO   | Index | Overlaid | Interface   | Remark |

|--------|-------|----------|-------------|--------|

| GPIO67 | —     | ALT1     | SD/MMC_CMD  | —      |

| GPIO68 | —     | ALT1     | SD/MMC_CK   | —      |

| GPIO69 | —     | ALT1     | SD/MMC_D0   | —      |

| GPIO70 |       | ALT1     | SD/MMC_D1   | —      |

| GPIO71 | —     | ALT1     | SD/MMC_D2   | —      |

| GPIO72 | —     | ALT1     | SD/MMC_D3   | —      |

| GPIO73 | —     | ALT1     | SD/MMC_D4   | —      |

| GPIO74 | —     | ALT1     | SD/MMC_D5   | —      |

| GPIO75 | _     | ALT1     | SD/MMC_D6   | —      |

| GPIO76 | _     | ALT1     | SD/MMC_D7   | —      |

| GPIO77 |       | ALT1     | SD/MMC_RSTN |        |

# 4.3 ETHERNET PORTS

LAN9668 has eight logical Ethernet ports. Two SerDes interfaces running QSGMII are used to connect each LAN8814 QuadPHY. The QSGMII signals are AC-coupled to ensure Common-mode voltage compatibility.

#### 4.3.1 Port Mapping

Software mapping between internal ports and front ports compensates for the physical board routing of PHY ports in the 2x4 ICM together with their MII-Management addresses, so ports appear like in Figure 3-2 from a user-management perspective.

Mapping:

| Port | Chip Port | MIIM Bus | MIIM Addr |

|------|-----------|----------|-----------|

| 0    | 2         | 0        | 9         |

| 1    | 3         | 0        | 10        |

| 2    | 0         | 0        | 7         |

| 3    | 1         | 0        | 8         |

| 4    | 6         | 0        | 17        |

| 5    | 7         | 0        | 18        |

| 6    | 4         | 0        | 15        |

| 7    | 5         | 0        | 16        |

|      |           |          |           |

#### 4.3.2 PHY Copper Interface

The LAN8814 QuadPHY integrates all passive components required to connect the PHYs' line-side interface to an external 1:1 transformer and Common-mode choke. This reduces the number of components in a design and greatly simplifies the layout of this interface.

The PHYs support auto-negotiation and downshift, and can automatically detect the speed of a link if auto-negotiation is disabled, and hereby provides the appropriate connection (parallel detect).

The PHYs include Automatic Crossover Detection functionality for all speeds (HP Auto MDI/MDI- X<sup>™</sup> function) and the ability to detect and correct polarity errors on all MDI pairs. These functions are normally enabled but can be disabled.

Instead of separate magnetic modules and RJ45 connectors, the reference board uses RJ45 connectors with integrated magnetics. This reduces the number of components on the board and the actual board area.

All PHYs support the IEEE standard range of 1m to 100m twisted pair cable; however:

- 1000BASE-T mode requires Category 5 enhanced cable in accordance to the cabling specifications defined by IEEE802.3-2005.

- 100BASE-TX mode requires Category 5 cable and 10BASE-T requires Category 3 cable as specified in ISO/IEC 11801.

#### 4.3.3 ICM - Integrated Magnetics

The reference board uses a 2x4 RJ45 ICM with integrated LEDs.

Note: The magnetics have huge influence on the EMI performance.

#### 4.3.4 MII-Management

The LAN9668 serves the LAN8814 QuadPHYs over a MIIM bus interface available as alternate function on its GPIO pins. The MIIM is daisy-chained to the two LAN8814 QuadPHYs covering front ports 1-8 and terminated at the end using pull-up on MDIO0 and split end-termination on MDC0. The drive strength for MDC0 is 3.

### 4.3.5 Thermal Diode (Optional)

The reference board can optionally provide a probe point using a 2-pin header to access the LAN8814 QuadPHY built-in thermal diode.

#### 4.3.6 Port LEDs and COMA Signal

Port LEDs are automatically controlled by the LAN8814 QuadPHY. There are two LEDs per port. One LED is for 1G traffic and the other is for 10/100M traffic. A solid ON LED means linkup, while blinking means traffic.

The PHY COMA input signal is used to suppress all errors, alarms, link-up/-down notifications until the PHY or the whole system has been properly initialized. The COMA signal is also being used to 'synchronize' the two LAN8814 LED blink rates.

The COMA signal can be controlled by software from either the LAN9668 or the two LAN8814.

#### 4.3.7 Optional Clock Scheme

The EVB-LAN9668 reference design provides an optional clocking scheme, where SyncE and IEEE 1588 timestamping are not an application requirement, and thus avoid populating the ZL30772 DPLL.

The clocking scheme leverages on the LAN8814 ability to provide an output clock from its internal PLL circuitry. This means:

25 MHz crystal → LAN8814#1 → CK25OUT → LAN8814#2 → CK25OUT → LAN9668

Using only one clock source and no clock buffer saves costs, and all devices still run on the same frequency, which prevents inter-packet gap shrinks in the TX direction and only one rate adaptation in the RX direction incoming traffic.

The default board setup is to use the ZL30772 DPLL provided reference clocks.

**Note:** Currently an errata prevents this clock scheme to work, as both LAN9668 and LAN8814 require a 125 MHz reference clock when using QSGMII.

#### 4.4 TIMING AND SYNCHRONIZATION

The reference board includes a factory preprogrammed DPLL, ZL30772-LFG7Q091 for frequency multiplier and clock buffer. It provides 25 MHz LVCMOS to the LAN9668 and 125 MHz LVDS-level reference clocks to LAN9668 and LAN8814. The ZL30772 is using a 114.285 MHz oscillator. For increased frequency stability, it can also operate in split-XO mode (see the *ZL30772 Data Sheet*) together with a 25 MHz TCXO.

The ZL30772 is controlled through the SPI interface using FLEXCOM 3 mode A. Optionally, it can be setup for  $I^2C$ .

#### 4.4.1 SyncE

For SyncE, the ZL30772 DPLL prioritizes and selects the clock source under software control and attenuates jitter before presenting the resulting clocks. The clock source can be either the free-running oscillators or a clock recovered from one of the CuPHY ports.

#### 4.4.2 Recovered Clock Multiplexing

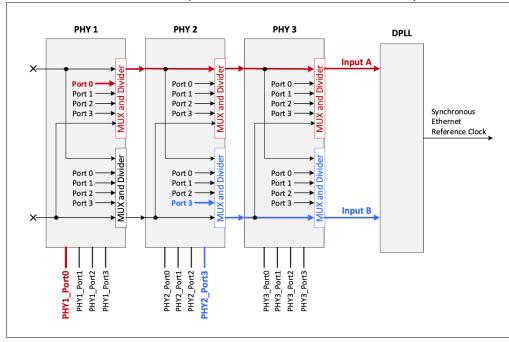

Each LAN8814 QuadPHY can do clock multiplexing and daisy-chaining of two selected recovered clocks to the ZL30772 DPLL inputs, as depicted in Figure 4-7.

#### FIGURE 4-7: DAISY-CHAINING RECOVERED OUTPUT CLOCKS USING LAN8814 (EXAMPLE SHOWING THREE PHYS)

### 4.4.3 PTP/IEEE1588v2

The free-running oscillators provide the base clock to the board DPLL. The XO can be exchanged with an OCXO for applications with higher requirements, and thus offering Stratum-3 holdover.

PTP interfacing is available through all network ports with timestamping in the LAN8814 QuadPHY and through input and output of 1PPS SMA connectors.