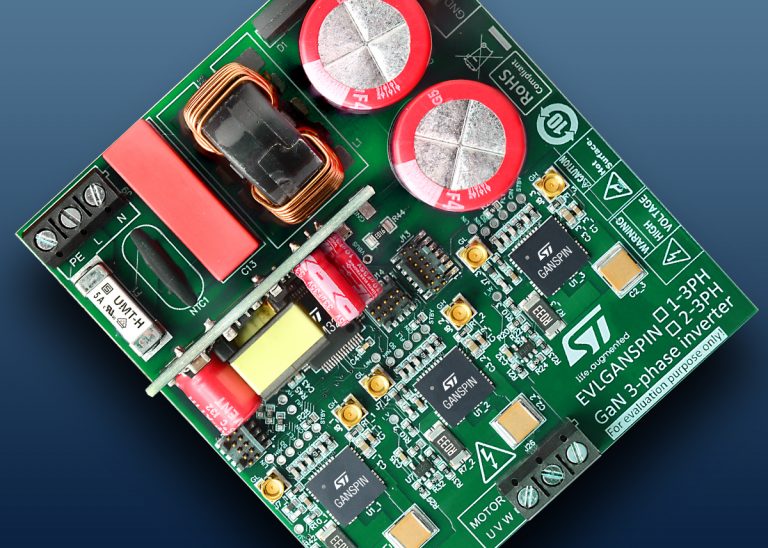

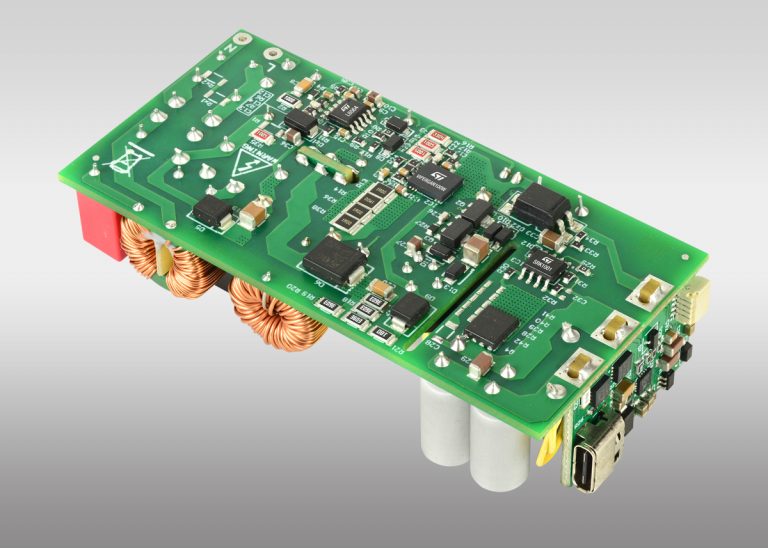

The EVLSTGAP3SXS-H is a half-bridge evaluation board designed to evaluate the STGAP3SXS isolated single gate driver for SiC MOSFETs.

The STGAP3SXS offers 10A current capability, rail-to-rail outputs and optimized UVLO and desaturation protection thresholds for SiC MOSFETS. This makes the STGAP3SXS optimal for high-power motor drivers in industrial applications.

The gate driver has a single output pin and a driver line for an external Miller clamp N-channel MOSFET, which optimizes the suppression of positive and negative gate spikes during fast commutations in half-bridge topologies.

The board is supplied by the 5V VAUX connection, which feeds the isolated dc-dc converters for the low-side and high-side driving sections. The gate drivers can be directly supplied by VAUX if a 5V MCU is used, or by the onboard linear regulator if a 3.3V MCU is used. The PWM and Reset inputs can be easily controlled through dedicated connectors while diagnostic outputs are connected to an onboard LED.

Device protection features for desaturation, soft turn-off, and Miller clamp are connected to the recommended network on the board and can be easily evaluated through the board test points.

Dual input pins allow the selection of signal polarity control and implementation of HW interlocking protection to avoid cross-conduction in case of controller malfunction.

The STGAP3SXS allows the implementation of negative gate driving, and the onboard isolated dc-dc converters allow working with optimized driving voltage for SiC MOSFETs.

The EVLSTGAP3SXS-H board allows evaluating all of the STGAP3SXS features while operating with a bus voltage up to 520V. It is possible to increase the bus voltage up to 1200V by replacing the two SiC MOSFETs with appropriate devices in a HiP247-4 package and the C4 capacitance if needed.